Some technical details.

I can't call it an "FAQ list" as nobody

asked these questions yet. So here are just the answers.

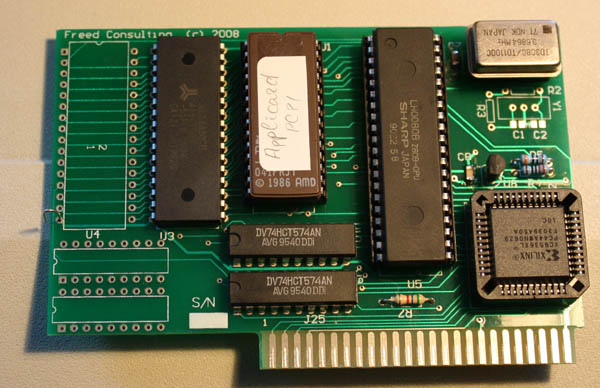

1. 74HCT574 octal flip-flops are used. Can be replaced by LS or F

version, but HC is not good as inputs comes from the Apple system bus -

TTL level. HCT is the best as it doesn't take much power and higher

speed is not needed.

2. The chip used for clock generation is on the contrary used from the

HC series. It produces a much cleaner clock in terms of symmetry than

an HCT version.

3. One NAND gate is used to combine A14 and A13 lines to implement a

common memory block. The original card has a jumper to select the

size of the common block - 8K or 16K. By default my card is configured

for an 8K size. To reconfigure for a 16K size R8 should be populated

and the trace cut between the pads labeled "8/16". You can later

install a jumper there to switch between the 8 and 16K.